## PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL FACULTY OF INFORMATICS COMPUTER SCIENCE GRADUATE PROGRAM

## A LIGHTWEIGHT VIRTUALIZATION LAYER WITH HARDWARE-ASSISTANCE FOR EMBEDDED SYSTEMS

## **CARLOS ROBERTO MORATELLI**

Dissertation submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fullfillment of the requirements for the degree of Ph. D. in Computer Science.

Advisor: Prof. Fabiano Hessel

# Ficha Catalográfica

### M831L Moratelli, Carlos Roberto

A lightweight virtualization layer with hardware-assistance for embedded systems / Carlos Roberto Moratelli . – 2016.

155 f.

Tese (Doutorado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. Fabiano Hessel.

1. Virtualization. 2. Embedded Systems. 3. Hypervisor. 4. Real-time. I. Hessel, Fabiano. II. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a).

# Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

## TERMO DE APRESENTAÇÃO DE TESE DE DOUTORADO

Tese intitulada "A Lightweight Virtualization Layer with Hardware-Assistance for Embedded Systems" apresentada por Carlos Roberto Moratelli como parte dos requisitos para obtenção do grau de Doutor em Ciência da Computação, aprovada em 22 de março de 2016 pela Comissão Examinadora:

| Kater Harl                                                  |                  |

|-------------------------------------------------------------|------------------|

| Prof. Dr. Fabiano Passuelo Hessel-<br>Orientador            | PPGCC/PUCRS      |

| Vialo terres                                                |                  |

| Prof. Dr. Tiago Coelho Ferreto –                            | PPGCC/PUCRS      |

| QQQ.                                                        |                  |

| Prof. Dr. Rômulo Silva de Oliveira -                        | UFSC             |

| )                                                           |                  |

| Radold Bered                                                |                  |

| Prof. Dr. Rodolfo Jardim de Azevedo -                       | UNICAMP          |

|                                                             |                  |

| Homologada em 66//2016, conforme Ata No. 9<br>Coordenadora. | 20 pela Comissão |

| Meanand                                                     |                  |

| Prof. Dr. Luiz Gustavo Leão Fernandes                       |                  |

| Coordenador.                                                |                  |

Campus Central

Av. Ipiranga, 6681 – P. 32 – sala 507 – CEP: 90619-900

Fone: (51) 3320-3611 - Fax (51) 3320-3621

PÓS-GRADUAÇÃO EM

CIÊNCIA DA COMPUTAÇÃO

E-mail: ppgcc@pucrs.br

www.pucrs.br/facin/pos

PROGRAMA DE

"I'm doing a (free) operating system (just a hobby, won't be big and professional like gnu) for 386(486) AT clones." (Linus Torvalds)

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to those who helped me throughout all my Ph.D. years and made this dissertation possible. First of all, I would like to thank my advisor, Prof. Fabiano Passuelo Hessel, who has given me the opportunity to undertake a Ph.D. and provided me invaluable guidance and support in my Ph.D. and in my academic life in general. Thank you to all the Ph.D. committee members – Prof. Carlos Eduardo Pereira (dissertation proposal), Prof. Rodolfo Jardim de Azevedo, Prof. Rômulo Silva de Oliveira and Prof. Tiago Ferreto - for the time invested and for the valuable feedback provided. Thank you Dr. Luca Carloni and the other SLD team members at the Columbia University in the City of New York for receiving me and giving me the opportunity to work with them during my 'sandwich' research internship.

Eu gostaria de agraceder minha esposa, Ana Claudia, por ter estado ao meu lado durante todo o meu período de doutorado. O seu apoio e compreensão foram e continuam sendo muito importantes para mim. Obrigado pela paciência, amor e carinho durante todos esses anos. Também gostaria de agradecer aos meus pais e irmão pelo apoio durante toda a minha vida. Agradeço aos colegas e amigos do laboratório GSE/PUCRS, especialmente ao amigo Sergio Johann Filho pelas importantes discusões durante a execução do trabalho.

# UMA CAMADA LEVE DE VIRTUALIZAÇÃO ASSISTIDA POR HARDWARE PARA SISTEMAS EMBARCADOS

#### **RESUMO**

O poder de processamento presente nos sistemas embarcados modernos permite a adoção de técnicas de virtualização. Juntamente com os ganhos em redução de custo e melhor utilização dos recursos, como por exemplo uma melhor utilização do processador, a virtualização possibilita a co-execução de diferentes sistemas operacionais em um processador, sejam eles sistemas operacionais de tempo real (RTOS) e/ou de propósito geral (GPOS). A implementação da técnica de virtualização esta baseada em um módulo de software denominado hypervisor.

Devido a complexidade de se desenvolver uma nova camada de virtualização especialmente projetada para sistemas embarcados, muitos autores propuseram modificações em sistemas de virtualização que são largamente empregados em servidores na nuvem para melhor adapta-los às necessidades dos sistemas embarcados. Contudo, a utilização de memória e os requisitos temporais de alguns dispositivos embarcados requerem abordagens diferentes daquelas utilizadas em servidores. Além disso, a atual tendência de utilização de virtualização nos dispositivos projetados para a internet das coisas (do inglês Internet of Things - IoT) aumentou o desafio por hypervisors mais eficientes, em termos de memória e processamento. Estes fatores motivaram o surgimento de diversos hypervisors especialmente projetados para atender os requisitos dos atuais sistemas embarcados.

Nesta tese, investigou-se como a virtualização embarcada pode ser melhorada a partir de seu estado atual de desenvolvimento para atender as necessidades dos sistemas embarcados atuais. Como resultado, propõe-se um modelo de virtualização capaz de agregar os diferentes aspectos exigidos pelos sistemas embarcados. O modelo combina virtualização completa e para-virtualização em uma camada de virtualização híbrida, além da utilização de virtualização assistida por hardware. Uma implementação baseada neste modelo é apresentada e avaliada. Os resultados mostram que o hypervisor resultante possui requisitos de memória compatíveis com os dipositivos projetados para IoT. Ainda, GPOSs and RTOS podem ser executados mantendo-se o isolamento temporal entre eles e com o baixo impacto no desempenho.

**Palavras-Chave:** Virtualização, Sistemas Embarcados, Hypervisor, Tempo-real.

# A LIGHTWEIGHT VIRTUALIZATION LAYER WITH HARDWARE-ASSISTANCE FOR EMBEDDED SYSTEMS

#### **ABSTRACT**

The current processing power of modern embedded systems enable the adoption of virtualization techniques. In addition to the direct relationship with cost reduction and better resource utilization, virtualization permits the integration of real-time operating systems (RTOS) and general-purpose operating systems (GPOS) on the same hardware system. The resulting system may inherit deterministic time response from the RTOS and a large software base from the GPOS. However, the hypervisor must be carefully designed.

Due to the complexity of developing a virtualization layer designed specially for embedded systems from scratch, many authors have proposed modifications of the widely used server virtualization software to better adapt it to the particular needs of embedded system. However, footprint and temporal requisites of some embedded devices require different approaches than those used in server farms. Also, currently virtualization is being adapted for the field of the Internet of Things (IoT), which has increased the challenge for more efficient hypervisors. Thus, a generation of hypervisors focused on the needs of embedded systems have emerged.

This dissertation investigated how embedded virtualization can be improved, starting from the current stage of its development. As a result, it is proposed a virtualization model to aggregate different aspects required by embedded systems. The model combines full and para-virtualization in a hybrid virtualization layer. In addition, it explores the newer features of embedded processors that have recently adopted hardware-assisted virtualization. A hypervisor implementation based on this model is presented and evaluated. The results show that the implemented hypervisor has memory requirements compatible with devices designed for IoT. Moreover, general-purpose operating systems and real-time tasks can be combined while keeping them temporally isolated. Finally, the overall virtualization overhead is for most part lower than in other embedded hypervisors.

**Keywords:** Virtualization, Embedded Systems, Hypervisor, Real-time.

# LIST OF FIGURES

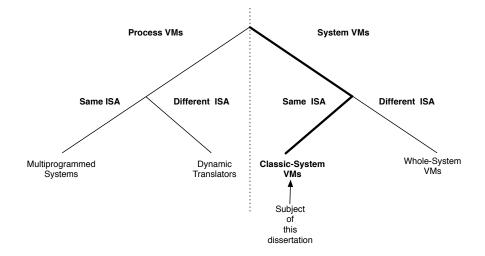

| 2.1  | A taxonomy of Virtual Machines. Classic-system VMs are the subject of study of this dissertation. Adapted from [70]                                          | 34 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

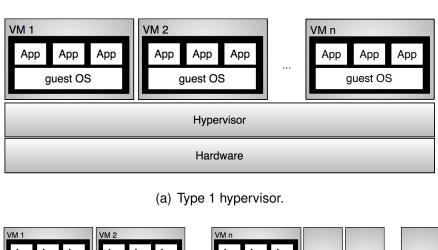

| 2.2  | Types of hypervisors                                                                                                                                         | 36 |

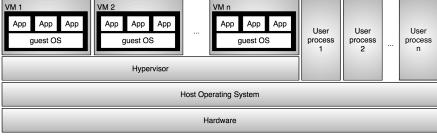

| 2.3  | Illustrating Popek and Goldbergs's Theorem. Adapted from [70]                                                                                                | 38 |

| 2.4  | Relation between hypercalls on a virtualized system and syscalls on a typical operating system.                                                              | 39 |

| 2.5  | Supervisor privileged level for hypervisor execution                                                                                                         | 42 |

| 2.6  | Memory virtualization approaches in non-virtualized versus virtualized systems                                                                               | 43 |

| 2.7  | Comparison of the IOMMU to the MMU                                                                                                                           | 45 |

| 3.1  | Xen's Architecture. Adapted from [9]                                                                                                                         | 52 |

| 3.2  | KVM's Architecture.                                                                                                                                          | 59 |

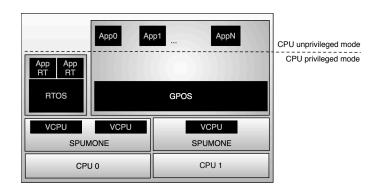

| 3.3  | SPUMONE's single-core Architecture. Adapted from [39]                                                                                                        | 66 |

| 3.4  | SPUMONE's multicore Architecture. Adapted from [51]                                                                                                          | 66 |

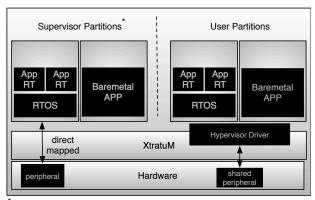

| 3.5  | XtratuM's architecture. It is a type 1 hypervisor designed for safety critical systems. Adapted from [19]                                                    | 68 |

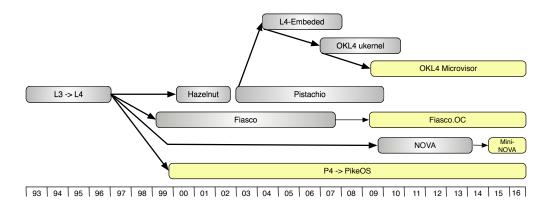

| 3.6  | Summarized L4 microkernel family tree that resulted in embedded hypervisors. Adapted from [25]                                                               | 69 |

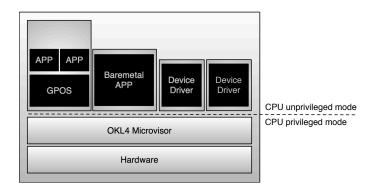

| 3.7  | OKL4's architecture. It was developed targeting mobile devices supporting several mobile OSs, and it powered the first commercial virtualized phone in 2009. | 70 |

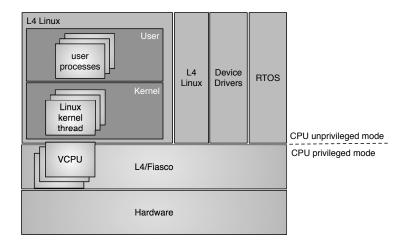

| 3.8  | Fiasco's architecture. The L4/Fiasco maps the L4Linux kernel threads directly to VCPUs.                                                                      | 71 |

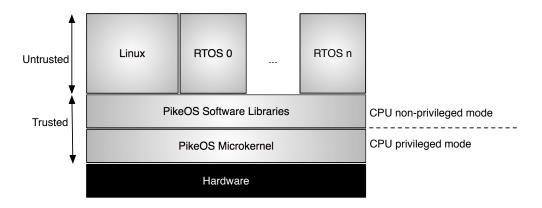

| 3.9  | PikeOS's architecture. It is a proprietary microkernel with support for virtualization designed to attend safety-critical systems                            | 72 |

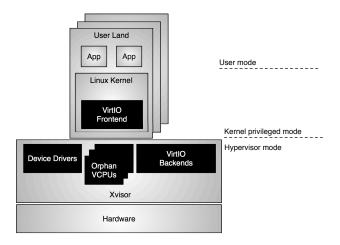

| 3.10 | Xvisor's architecture. The Xvisor hypervisor uses the third privileged level from ARM's architecture.                                                        | 74 |

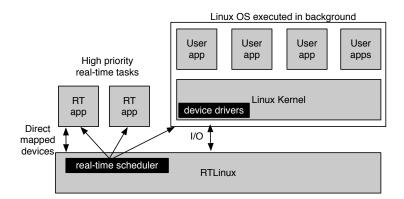

| 3.11 | RT-Linux is a kernel patch that adds a software layer with a real-time scheduler and it makes the Linux kernel to share the processor with real-time |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | tasks                                                                                                                                                |

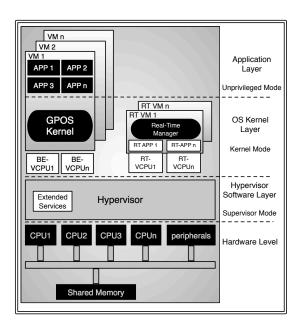

| 4.1  | Overall view of the proposed virtualization model 83                                                                                                 |

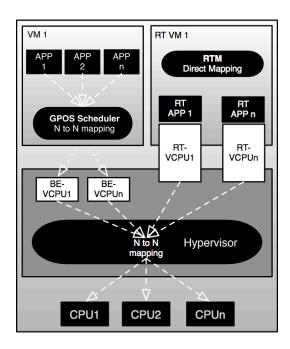

| 4.2  | Flexible mapping for multiprocessor embedded systems with real-time sup-                                                                             |

|      | port                                                                                                                                                 |

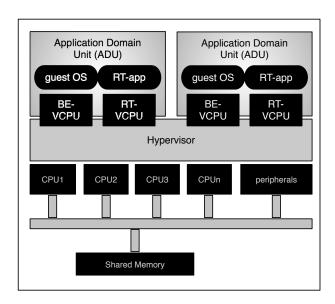

| 4.3  | Virtual Hellfire Hypervisor's virtualization model                                                                                                   |

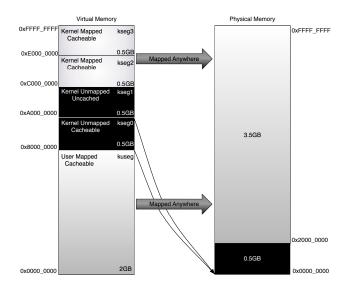

| 5.1  | MIPS32 memory map                                                                                                                                    |

| 5.2  | Hypervisor's software block diagram                                                                                                                  |

| 5.3  | Example of the scheduling strategy to combine the EDF and best-effort schedulers                                                                     |

| 5.4  | Virtual memory organization view of our hypervisor                                                                                                   |

| 5.5  | Quantum scheduler scheme for interrupt delivery                                                                                                      |

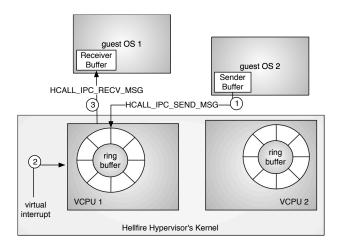

| 5.6  | Example of inter-VM communication involving two guests                                                                                               |

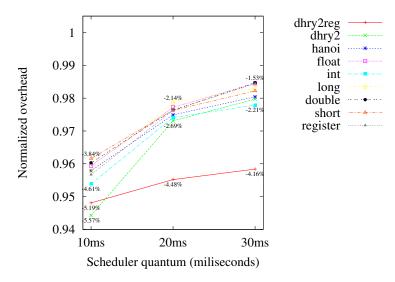

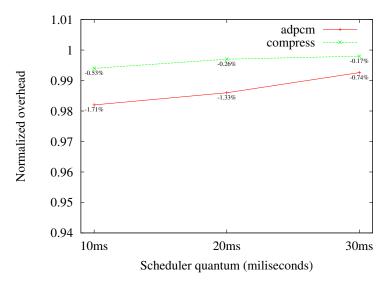

| 6.1  | Performance overhead for user-land applications relative to non-virtualized                                                                          |

|      | performance                                                                                                                                          |

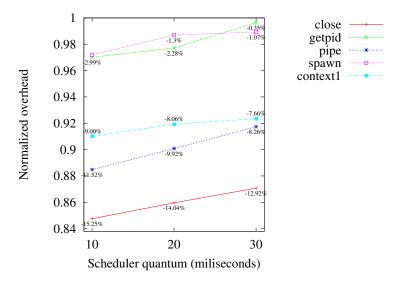

| 6.2  | Performance overhead for syscall applications relative to non-virtualized                                                                            |

|      | performance                                                                                                                                          |

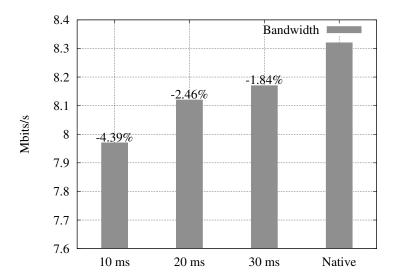

| 6.3  | Iperf bandwidth results for TCP protocol comparing native versus virtualized                                                                         |

|      | execution with different hypervisor's scheduler quantum                                                                                              |

| 6.4  | Performance overhead for CPU intensive applications relative to non-virtualized                                                                      |

|      | performance                                                                                                                                          |

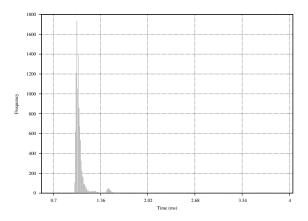

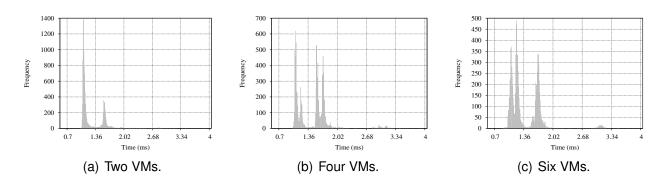

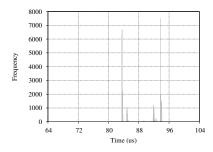

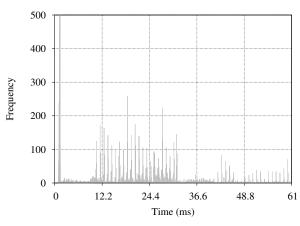

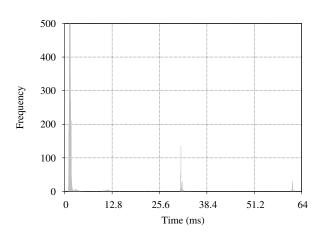

| 6.5  | Histogram for RTT of the messages for native execution of the Linux/MIPS 123                                                                         |

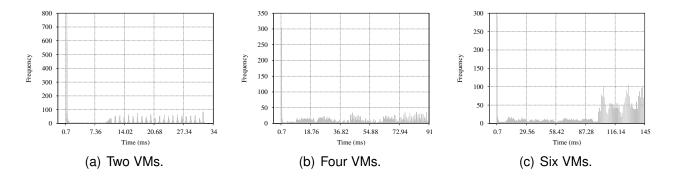

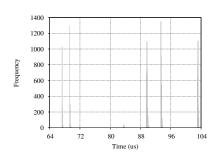

| 6.6  | Histogram for RTT of the messages without policy                                                                                                     |

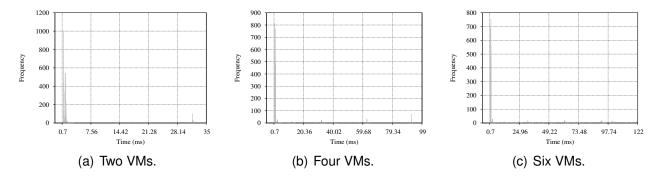

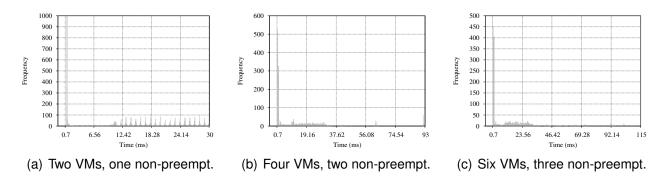

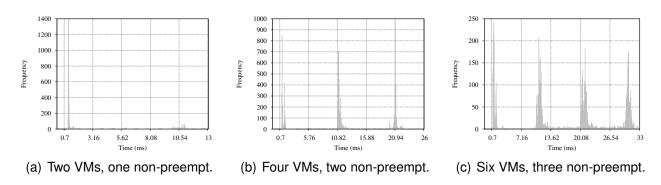

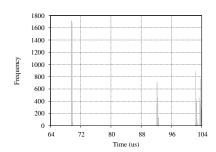

| 6.7  | Histogram for RTT of the messages with fast interrupt policy and quantum                                                                             |

|      | recycling                                                                                                                                            |

| 6.8  | Histogram for RTT of the messages with fast interrupt policy and quantum                                                                             |

|      | reset                                                                                                                                                |

| 6.9  | Histogram for RTT of the messages with fast interrupt policy and quantum                                                                             |

|      | recycling with non-preemptable VCPUs.                                                                                                                |

| 6.10 | Histogram for RTT of the messages with fast interrupt policy and quantum          |

|------|-----------------------------------------------------------------------------------|

|      | reset with non-preemptable VMs                                                    |

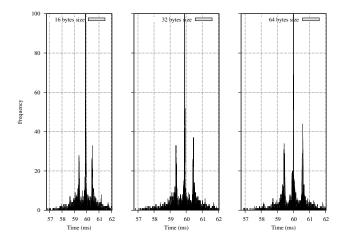

| 6.11 | RTT's histograms for inter-VM communication using the Hellfire Hypervisor         |

|      | communication mechanism                                                           |

| 6.12 | Histogram of the execution delay for RT-VCPUs in microseconds                     |

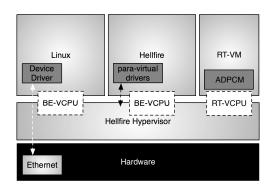

| 6.13 | System configuration for the ADPCM execution                                      |

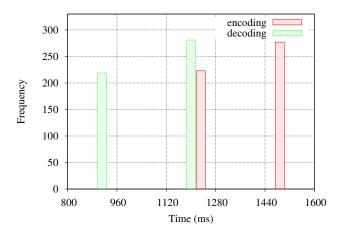

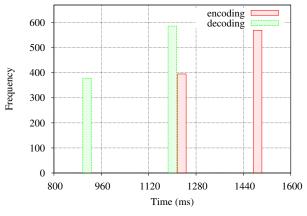

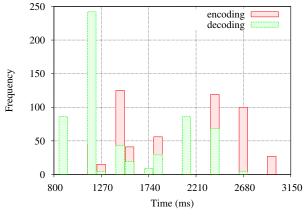

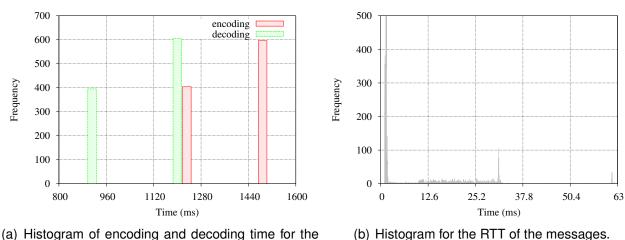

| 6.14 | Histogram of encoding and decoding execution time for the ADPCM algo-             |

|      | rithm without external interferences                                              |

| 6.15 | System response time without the fast interrupt deliver policy and a pre-         |

|      | emptable RT-VM                                                                    |

| 6.16 | System response time with the fast interrupt deliver policy and a preempt-        |

|      | able RT-VM                                                                        |

| 6.17 | System response time with the fast interrupt deliver policy and a non-preemptable |

|      | RT-VM                                                                             |

# LIST OF TABLES

| 2.1 | Example of embedded systems market and devices. Adapted from [55]                                            | 32  |

|-----|--------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Embedded hypervisors' comparative table                                                                      | 75  |

| 3.2 | Footprint requirements for Xen and KVM                                                                       | 76  |

| 3.3 | Footprint requirements of the hypervisors when available                                                     | 76  |

| 4.1 | Hypercalls as extended services                                                                              | 86  |

| 5.1 | GuestClt0 register fields. These bits are used to control the hardware accessibility by the guest OS         | 98  |

| 5.2 | Example of a set of interrupt rules for a system configured with three guest                                 |     |

|     | OSs                                                                                                          | 105 |

| 5.3 | Example of memory mapping for a Linux and a HellfireOS guests                                                | 108 |

| 6.1 | Size of the hypervisor's segments. The sum of all segments is the footprint                                  |     |

|     | of the hypervisor during its execution                                                                       | 114 |

| 6.2 | Number of guest exceptions in the original and the modified Linux/MIPS                                       |     |

|     | guest during the boot                                                                                        | 116 |

| 6.3 | Average $(\overline{x})$ , standard deviation $(s)$ , median $(m)$ and $95^{th}$ percentile $(p^{th})$ for   |     |

|     | RTT of the messages in milliseconds for Linux native execution                                               | 122 |

| 6.4 | Average $(\overline{x})$ , standard deviation $(s)$ , median $(m)$ and $95^{th}$ percentile $(p^{th})$ for   |     |

|     | RTT of the messages in milliseconds for virtualized Linux execution                                          | 122 |

| 6.5 | Average $(\overline{x})$ , standard deviation $(s)$ , median $(m)$ and $95^{th}$ percentile $(p^{th})$ for   |     |

|     | the execution delay on the EDF scheduler in microseconds                                                     | 128 |

| 6.6 | Average $(\overline{x})$ , standard deviation $(s)$ , median $(m)$ , $95^{th}$ percentile $(p^{th})$ , worst |     |

|     | execution case (WEC) and best execution case (BEC) to ADPCM encoding                                         |     |

|     | and decoding and the RTT of the messages for different system configura-                                     | 100 |

|     | tions in milliseconds                                                                                        | 130 |

# **LIST OF ACRONYMS**

| ABI – Application Binary Interface                    |

|-------------------------------------------------------|

| ADPCM – Adaptive Differential Pulse-code Modulation   |

| ADU – Application Domain Unit                         |

| API – Application Programming Interface               |

| BEC – Best Execution Case                             |

| BE-VCPU – Best-effort Virtual Central Processing Unit |

| BVT – Borrowed Virtual Time                           |

| CBS - Constant Bandwidth Server                       |

| CE – Costumer Electronic                              |

| CPU - Central Processing Unit                         |

| CP0 – Coprocessor 0                                   |

| CSA – Compositional Scheduling Architecture           |

| DMA – Dynamic Memory Access                           |

| DPR – Dynamic Partial Reconfiguration                 |

| DRAM – Dynamic Random-Access Memory                   |

| EDF – Earliest Deadline First                         |

| ES – Embedded System                                  |

| FP – Fixed Priority                                   |

| FV – Full-Virtualization                              |

| GCP0 – Guest Cooprocessor 0                           |

| GPOS – General Purpose Operating System               |

| GSE – Embedded Systems Group                          |

| GSM – Global System for Mobile Communications         |

| GuestCtl0 – Guest Control Register 0                  |

| HAL – Hardware Abstraction Layer                      |

| HLL – High Level Languages                            |

HVM - Hardware-assisted Virtualization

IASim - MIPS Instruction Accurate Simulator

IoT – Internet of Things

IPA – Intermediate Physical Address

ISA - Instruction Set Architecture

I/O – Input/Output

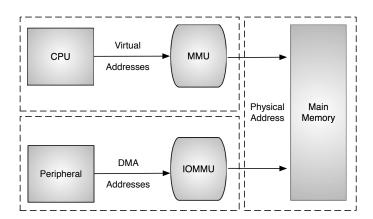

IOMMU - Input-output Memory Management Unit

JVM - Java Virtual Machine

NVRAM – Non-Volatile Random Access Memory

OS – Operating System

OVP - Open Virtual Platforms

PA - Physical Address

PID - Processor Identification

PV - Para-Virtualization

RTM - Real-time Manager

RTOS – Real-time Operating System

RT-VCPU – Real-time Virtual Central Processing Unit

SEDF – Simple Earliest Deadline First

USB - Universal Serial Bus

VA - Virtual Address

VCPU - Virtual Central Processing Unit

VHH – Virtual Hellfire Hypervisor

VM – Virtual Machine

VMM – Virtual Machine Manager

WEC - Worst Execution Case

# **CONTENTS**

| 1 |     | INTROI  | DUCTION                                           | 25         |

|---|-----|---------|---------------------------------------------------|------------|

|   | 1.1 | Hypotl  | hesis and Research Questions                      | 27         |

|   | 1.2 | Organ   | ization of This Dissertation                      | 28         |

| ^ |     |         | PROLING IN EMPERGED CYCTEMS AND VIDTUALIZATION    | 21         |

| 2 |     |         | ROUND IN EMBEDDED SYSTEMS AND VIRTUALIZATION      | 31         |

|   | 2.1 | Embe    | dded Systems                                      | 31         |

|   | 2.2 | What I  | Means Virtualization?                             | 33         |

|   |     | 2.2.1   | Types of Hypervisors                              | 35         |

|   |     | 2.2.2   | Requirements for Processor's Virtualization       | 37         |

|   | 2.3 | Enabli  | ng Techniques and Technologies for Virtualization | 38         |

|   |     | 2.3.1   | Para-virtualization                               | 38         |

|   |     | 2.3.2   | Full-virtualization                               | 40         |

|   |     | 2.3.3   | Hardware-assisted Virtualization                  | 41         |

|   |     | 2.3.4   | I/O Virtualization                                | 44         |

|   | 2.4 | Proble  | ems Caused by Virtualization                      | 45         |

|   |     | 2.4.1   | The Hierarchical Scheduling Problem               | 46         |

|   |     | 2.4.2   | Lock Holder Preemption Problem                    | 46         |

|   | 2.5 | Virtua  | lization for Embedded Systems                     | 47         |

|   | 2.6 | Past, F | Present and Future of Embedded Virtualization     | 48         |

| 3 |     | CTATE   | OF-THE-ART IN EMBEDDED VIRTUALIZATION             | <b>5</b> 1 |

| 3 |     |         |                                                   | 51         |

|   | 3.1 | The X   | en Hypervisor                                     | 51         |

|   |     | 3.1.1   | Xen's Architecture                                | 52         |

|   |     | 3.1.2   | The Xen Scheduling Algorithm                      | 53         |

|   |     | 3.1.3   | Xen-Based Proposals                               | 54         |

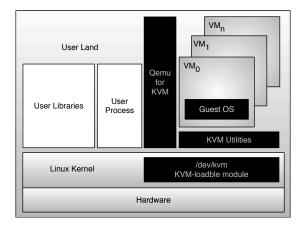

|   | 3.2 | KVM H   | Hypervisor                                        | 59         |

|   |     | 3.2.1   | KVM's Architecture                                | 59         |

|   |     | 3.2.2   | The Linux Scheduling Algorithm                    | 60         |

|   |            | 3.2.3                                                                                    | KVM-based proposals                                                                                                                                                                                                         | 62                                            |

|---|------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

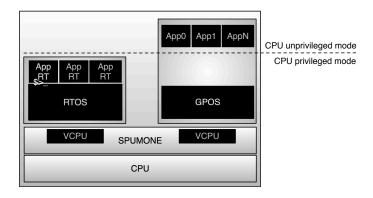

|   | 3.3        | SPUM                                                                                     | IONE                                                                                                                                                                                                                        | 65                                            |

|   | 3.4        | Xtratu                                                                                   | M                                                                                                                                                                                                                           | 67                                            |

|   | 3.5        | L4 Mid                                                                                   | crokernel Family based hypervisors                                                                                                                                                                                          | 69                                            |

|   |            | 3.5.1                                                                                    | OKL4 Microvisor                                                                                                                                                                                                             | 70                                            |

|   |            | 3.5.2                                                                                    | L4/Fiasco                                                                                                                                                                                                                   | 71                                            |

|   |            | 3.5.3                                                                                    | PikeOS                                                                                                                                                                                                                      | 72                                            |

|   |            | 3.5.4                                                                                    | Mini-Nova                                                                                                                                                                                                                   | 73                                            |

|   | 3.6        | М-Нур                                                                                    | pervisor                                                                                                                                                                                                                    | 73                                            |

|   | 3.7        | Xvisor                                                                                   |                                                                                                                                                                                                                             | 74                                            |

|   | 3.8        | Embe                                                                                     | dded Hypervisors Comparison                                                                                                                                                                                                 | 75                                            |

|   | 3.9        | RT-Lin                                                                                   | ux                                                                                                                                                                                                                          | 77                                            |

|   | 3.10       | Final (                                                                                  | Considerations                                                                                                                                                                                                              | 78                                            |

| 4 |            | A VIRT                                                                                   | UALIZATION MODEL FOR EMBEDDED SYSTEMS                                                                                                                                                                                       | 79                                            |

|   | 4.1        | Desira                                                                                   | uble Features for an Embedded Virtualization Model                                                                                                                                                                          | 79                                            |

|   |            |                                                                                          |                                                                                                                                                                                                                             |                                               |

|   | 4.2        | Model                                                                                    | Overview                                                                                                                                                                                                                    | 82                                            |

|   | 4.2        | Model                                                                                    | Overview                                                                                                                                                                                                                    | 82<br>84                                      |

|   | 4.2        | 4.2.1                                                                                    |                                                                                                                                                                                                                             | 84                                            |

|   | 4.2        | 4.2.1                                                                                    | The Flexible Scheduling Mapping                                                                                                                                                                                             | 84<br>84                                      |

|   | 4.2        | 4.2.1<br>4.2.2<br>4.2.3                                                                  | The Flexible Scheduling Mapping                                                                                                                                                                                             | 84<br>84<br>86                                |

|   | 4.2        | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                         | The Flexible Scheduling Mapping                                                                                                                                                                                             | 84<br>84<br>86                                |

|   |            | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp                                                 | The Flexible Scheduling Mapping                                                                                                                                                                                             | 84<br>84<br>86<br>88                          |

|   | 4.3        | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp                                                 | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations                                                               | 84<br>84<br>86<br>88                          |

| 5 | 4.3<br>4.4 | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp<br>Final (                                      | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations  IRE HYPERVISOR - AN IMPLEMENTATION USING MIPS HARDWARE-      | 84<br>84<br>86<br>88<br>88<br>90              |

| 5 | 4.3<br>4.4 | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp<br>Final (                                      | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations                                                               | 84<br>84<br>86<br>88                          |

| 5 | 4.3<br>4.4 | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp<br>Final (                                      | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations  IRE HYPERVISOR - AN IMPLEMENTATION USING MIPS HARDWARE-      | 84<br>84<br>86<br>88<br>88<br>90              |

| 5 | 4.3<br>4.4 | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp<br>Final (                                      | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations  IRE HYPERVISOR - AN IMPLEMENTATION USING MIPS HARDWARE-TANCE | 84<br>84<br>86<br>88<br>88<br>90              |

| 5 | 4.3<br>4.4 | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Comp<br>Final (<br>HELLF<br>ASSIST<br>The M<br>5.1.1 | The Flexible Scheduling Mapping  Extended Services  Real-time Aspects  Communication Model  arison with the Virtual Hellfire Hypervisor (VHH)  Considerations  IRE HYPERVISOR - AN IMPLEMENTATION USING MIPS HARDWARE-TANCE | 84<br>84<br>86<br>88<br>88<br>90<br><b>93</b> |

|   | 5.3 | CPU Virtualization Strategy                          | 97  |

|---|-----|------------------------------------------------------|-----|

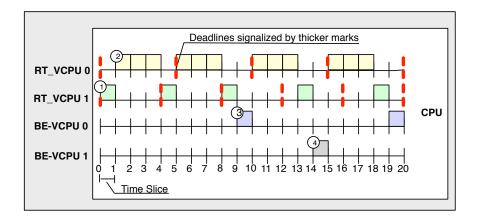

|   |     | 5.3.1 Best-effort and real-time scheduler algorithms | 99  |

|   |     | 5.3.2 Timer Virtualization                           | 100 |

|   | 5.4 | Virtual Memory Management                            | 101 |

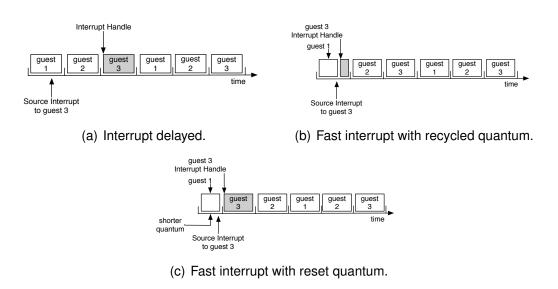

|   | 5.5 | Interrupt Virtualization                             | 103 |

|   |     | 5.5.1 Virtual Interrupt                              | 106 |

|   | 5.6 | Inter-VM Communication                               | 106 |

|   | 5.7 | Engineering Effort to Support a Guest OS             | 107 |

|   |     | 5.7.1 Linux and Hellfire OSs as Guests               | 108 |

|   | 5.8 | Current Hypervisor Restrictions                      | 109 |

|   | 5.9 | Final Considerations                                 | 110 |

| 6 | ı   | HYPERVISOR EVALUATION AND PRACTICAL RESULTS          | 113 |

| • | 6.1 | SEAD-3 Development Board                             |     |

|   | 6.2 | Hypervisor Memory Footprint                          |     |

|   | 6.3 | Linux Port Experience                                |     |

|   |     | Overhead Impact on Linux                             |     |

|   | 0.4 | 6.4.1 CPU-bound Benchmarks                           |     |

|   |     |                                                      |     |

|   | 6.5 |                                                      |     |

|   | 6.6 | Overhead Impact on HellfireOS                        |     |

|   | 6.7 |                                                      |     |

|   |     | Inter-VM Communication Response Time                 |     |

|   | 6.8 | Real-time Services Performance                       |     |

|   |     | 6.8.1 RT-VCPUs Execution Delay                       |     |

|   | 0.0 | 6.8.2 Interrupt Handling Interference on RT-VCPUs    |     |

|   | 6.9 | Final Considerations                                 | 133 |

| 7 |     | CONCLUSIONS                                          | 135 |

|   | 7.1 | Concluding Remarks                                   | 136 |

|   | 7.2 | Future Research                                      | 137 |

| 7.3 | List of Publications                                         | 138 |

|-----|--------------------------------------------------------------|-----|

|     | REFERENCES                                                   | 139 |

|     | APPENDIX A – Virtual Machine and Virtual CPU Data Structures | 149 |

| A.1 | Virtual Machine Data Structure                               | 149 |

| A.2 | VCPU Data Structure                                          | 150 |

### 1. INTRODUCTION

Embedded systems are being widely adopted in all areas of human activity. Their increased performance during recent years has enabled a wide range of new applications. However, more processing power implies more functionalities and increased software complexity, which directly impacts the design constraints and goals of embedded systems [85]. For example, the possibility for the final user to develop and download new applications, before exclusively found in general-purpose systems, can now be found in many modern embedded devices [31]. This scenario has forced designers and companies to adopt new strategies, such as increased use of software layers allowing for more flexible platforms capable of meeting timing, energy consumption, and time-to-market constraints. Although embedded systems are assuming many of the features of general-purpose systems, some differences remain. They present critical real-time constraints and frequently have resource constraints such as, limited battery, memory and processing power.

The appearance of server farms in the 1990s and the increasing performance of the computer systems stimulated the adoption of virtualization. Virtualization allows for the possibility of decoupling the one-to-one correspondence between hardware and software. Thus, keeping several different operating systems on the same computer system, can drastically reduce the maintenance and energy costs [54]. Different operating systems reside in a shared memory and are combined on a single or multi-core processor through a software stack called a virtual machine monitor or hypervisor. In recent years, virtualization technology has quickly moved towards embedded systems motivated by the increasing processing power of the embedded processors and the increasing challenges to comply with their requirements. Although server virtualization is a well-known and mature technology widely applied for commercial use, embedded system virtualization is still being studied and developed. The main restriction to broader use of virtualization for embedded systems is that their requirements differ from server and enterprise systems [65]. Most notably, timing constraints and limited resources, like CPU and memory, are the main concerns around embedded systems virtualization. Thus, virtualization as deployed in the enterprise environment cannot be directly used in embedded systems.

There are many studies proposing different techniques for embedded system virtualization. A common approach is to adapt hypervisors widely used in server virtualization to

embedded systems. The main concern about general purpose hypervisors is the absence of suitable support for real-time and memory requirements incompatible with some embedded devices. Despite these limitations, researchers are continually working to improve the embedded support of open-source hypervisors for server virtualization, like XEN and KVM, as seen in [22], [92], [89] and [8]. On the other hand, the distinguished characteristics of the embedded systems have motivated the appearance of hypervisors specially designed for embedded virtualization. Among the goals for embedded hypervisors development, two of them are frequently addressed: to keep low memory requirements and some level of support for real-time applications. Additionally, the diversity of embedded systems and their applications encourages the development of many different embedded hypervisors, like SPUMONE [39], Xtratum [80], M-Hypervisor [93], Xvisor [59] and the L4 hypervisors family [86], [32], [38], [88].

Intel and AMD manufactures provided hardware support for virtualization on the x86 architecture to address the continuous adoption of server virtualization. This was aimed to simplify the virtualization software layer and to improve performance. Before hardwareassisted virtualization, hypervisors needed to implement a technique called para-virtualization that consists of modifying the operating system to be virtualized. These operating system modifications break the software compatibility and require additional engineering work along with licence and source-code access for proprietary software. With dedicated hardware for virtualization, the hypervisors could implement a technique called full-virtualization where no modifications are required on the target operating system. Thus, making it easier to support new operating systems, especially proprietary ones. Similar to the x86 architecture, the late adoption of hardware-assisted virtualization for embedded processors made para-virtualization rule the development of embedded virtualization. Nowadays, the main embedded processor manufacturers had already designed virtualization extensions for their processor families, like PowerPC [26], ARM [6] and MIPS [36]. These gave hypervisor developers more design choices. Modern hardware-assisted virtualization now makes it possible to virtualize an operating system without any modification and keeps performance close to the level of non-virtualized systems. This is important to support legacy software. However, advanced hypervisor features like communication among virtual machines or shared devices may still require para-virtualization technique.

This dissertation starts by addressing the different embedded virtualization approaches and discussing their drawbacks and advantages. It points to several features

required for embedded virtualization that the current hypervisor approaches fail to support. Thus, it is proposed the hybrid virtualization model concept that combines full and para-virtualization in the same hypervisor. To support full-virtualization, the model considers the recent hardware-assisted virtualization adopted in some embedded processors. Para-virtualization is used for extended services, such as communication among virtual machines, and real-time services. A hypervisor implementation based on the proposed model was developed for the MIPS M5150 processor and evaluated in the SEAD-3 development board. The contribution of this Ph.D. research is to show how design choices based on hardware-assisted virtualization associated with embedded system characteristics result in a simpler hypervisor, while still improving overall performance of the whole system.

## 1.1 Hypothesis and Research Questions

The aim of this work is to investigate the hypothesis that is possible to have an embedded lightweight hypervisor capable of supporting the major embedded virtualization requisites. Moreover, if considered that this hypothesis can be true, how important is the new hardware-assisted virtualization to accomplish it? Fundamental research questions associated with the hypothesis that guided this research are defined as follows:

- 1. What is the state-of-the-art in embedded virtualization and how does it accomplish the needs of embedded systems? This research question's main objective is to study embedded virtualization in detail and identify where the current virtualization models fail to support virtualization for embedded systems. Answering this research question will make it possible to understand the approaches that have already been tested, identify their limitations, and point out opportunities for improvements.

- 2. Can a virtualization model embrace the major embedded systems' needs and what features does it need to support to accomplish this goal? The objective of this research question is to determine the required embedded virtualization features and to propose a virtualization model capable of supporting these features. It is important to understand how different features, some of them contradictory, can be combined in the same model. The resulting virtualization model will guide the development of a new embedded hypervisor.

3. Can an implementation from a virtualization model be trustworthy and how can hardware-assisted virtualization be used to achieve this goal? This research question addresses whether a practical implementation can be constructed from the proposed virtualization model. Theoretical models can be hard to implement or an implementation may not achieve the expected results.

### 1.2 Organization of This Dissertation

The remainder of this dissertation is organized as follows:

- Chapter 2 explains the basic concepts for the best understanding of the remainder of the text. It starts by defining embedded systems and their applications. Virtualization is defined along with a taxonomy of virtual machines. The different types of hypervisors are shown and the requirements for virtualizing a processor are explained. The technologies that make virtualization possible are also discussed. Moreover, two critical problems resulting from virtualization usage are presented. Then, the relationship between virtualization and embedded systems is explained. Finally, it discusses the past, present and future possibilities for virtualization in embedded systems.

- Chapter 3 describes the state-of-the-art in embedded virtualization. The chapter starts by showing hypervisors designed for server virtualization. Then it presents several different authors' proposals to adapt these hypervisors for embedded systems. Subsequently, different hypervisors developed specially for embedded systems are described. A comparative study about the hypervisors is then presented. Finally, a Linux approach to improve real-time responsiveness is explained and compared to virtualization. Chapter 3 addresses research question (1).

- Chapter 4 presents the virtualization model proposed in this dissertation. First, it discusses the required features for a virtualization model for embedded systems. Then, the proposed embedded virtualization model is presented, and its different aspects are discussed. Finally, the model is compared to the Virtual Hellfire Hypervisor's model (VHH is a hypervisor previously developed in the Embedded Systems Group at PUC-RS). Chapter 4 addresses research question (2).

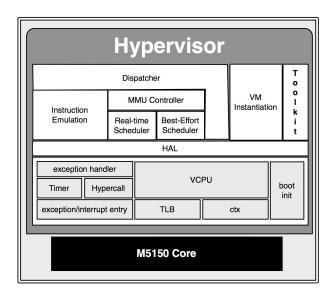

- Chapter 5 describes the hypervisor implementation based on the virtualization model proposed. First, the processor supported by the hypervisor is briefly presented. The software architecture is discussed and the CPU virtualization strategy is explained. Then the memory virtualization approach is exposed and the strategy for interrupt handling is described. The mechanism to allow communication among virtual machines is explained. Finally, the engineering effort to support a new guest and the implementation restrictions are discussed. Chapter 5 partially addresses research question (3).

- Chapter 6 shows the hypervisor evaluation and practical results. The hypervisor memory requirements are determined and compared to other hypervisors. Next, the experience to port Linux and minor modifications to the Linux kernel to improve performance is described. The overall hypervisor overhead impact is then analyzed. The interrupt delivery strategy and the communication mechanism among virtual machines are also evaluated. Moreover, the real-time capabilities are measured. Lastly the overall results are discussed. Chapter 6 concludes research question (3).

- Chapter 7 summarizes the dissertation and presents the concluding remarks. It restates the answers to the research questions, the main contributions, and presents possible directions for future work.

# 2. BACKGROUND IN EMBEDDED SYSTEMS AND VIRTUALIZATION

This chapter explains basic concepts to better understand the remainder of the text. Virtualization is a complex subject that involves several different topics and a wide range of solutions. This dissertation focuses on virtualization for the embedded systems. Thus, Section 2.1 starts by explaining the concept of embedded systems. If the reader is familiar with the definition of embedded systems, it is suggested that you read this chapter from Section 2.3. Section 2.2 introduces virtualization and its taxonomy, the different types of hypervisors and the requirements for virtualization. Section 2.3 explains different technologies that make virtualization possible. Section 2.4 describes two different problems caused by the use of virtualization. Section 2.5 shows the advantages of virtualization for embedded systems. Finally, Section 2.6 discusses the past, present and future of virtualization for embedded systems. If you are familiar with virtualization and embedded virtualization concepts, it is suggested to read this work from Chapter 3.

### 2.1 Embedded Systems

The use of microprocessors in equipment and consumer applications rather than laptop or personal computers (PCs) is wide spread. Actually, PCs are only one application of microprocessors. Embedded microprocessors are deeply integrated into everyday life, i.e., cars, microwaves oven, TVs, cell phones, and many other electronics are powered by microprocessors. Additionally, the increasing adoption of Internet of Things (IoT) [28] is accelerating the use of embedded applications. It is expected that there will be 24 billion interconnected devices by the year 2020 [28].

An embedded system (ES) is a computer system designed for a specific purpose, which distinguishes it from PCs or supercomputers. However, it is difficult to find a unique definition for ESs as they constantly evolve with advances in technology and as costs decrease. The following definition from [29] says: *An embedded system is a microprocessor-based system that is built to control a function or range of functions and is not designed to be programmed by the end user in the same way that a PC is.* Most embedded devices are

designed for a specific function. However, this definition sounds outdated as modern ESs may allow the final user to develop and download new applications, e.g., smartphones and smartTVs. Additionally, another definition highlights their reliability [55]: *An ES is a computer system with higher quality and reliability requirements than other types of computer systems.* This definition covers systems such as avionics or medical equipment where a malfunction is life-threatening. Due to the wide range of ES purposes, there is not a single definition. Table 2.1 shows examples of the embedded system markets and devices.

Table 2.1: Example of embedded systems market and devices. Adapted from [55].

| Market               | Embedded Device   |

|----------------------|-------------------|

|                      | Ignition system   |

| Automotive           | Air bag sensors   |

|                      | Engine control    |

|                      | Smart phones      |

|                      | Smart TVs         |

| Consumer electronics | Games             |

|                      | Toys              |

|                      | Laptops           |

| Industrial control   | Robotics          |

| Medical              | Cardiac monitors  |

| Iviedical            | Dialysis machines |

| Notworking           | Routers           |

| Networking           | Switches          |

| Office automation    | Printers          |

| Office automation    | Scanners          |

A recent trend in ESs is about their software complexity. Noergaard [55] defined ES software and application layers as optional. Thus, an ES could be composed of only a hardware layer. However, the performance improvement in functionalities, processing power and storage capacity over the last years has enabled a wide range of new complex applications and functionalities for ESs. Thus, the designers tend to adopt complex software layers to accomplish their goals. As mentioned early in this section, the possibility for the final user to develop and download new applications, before exclusively found in general-purpose systems, can now be found in many embedded devices. This has forced designers and companies to adopt new strategies, resulting in the increased use of software layers.

Although ESs are incorporating general-purpose features, many constraints remain. Because they are designed for specific functions, engineers can reduce the size and cost of the final product resulting in relatively simple and cheap devices. Thus, ES may suffer from hardware constraints, like reduced processing power, memory, weight and bat-

tery life. This added to the increasing complexity of embedded software is a challenge for designers that still need to meet timing, energy consumption, and time-to-market constraints for their products. In this scenario, virtualization can be a useful tool to deal with software complexity while increasing reuse, security and software quality.

### 2.2 What Means Virtualization?

Virtualization means the creation of an environment or, the creation of a virtual machine (VM), that acts like the real target hardware from the software or user point of view. The VM is implemented as a combination of real hardware and software aiming to execute applications [70]. Figure 2.1 depicts the taxonomy of VMs suggested by [70]. There are two kinds of VMs: process VMs and system VMs. Typically, a process VM is implemented on top of the operating system's (OS) application binary interface (ABI) and is able to emulate both user-level instructions and OS system calls for an individual process. A system VM provides a complete system environment capable of supporting an entire OS. Thus, a single computer can support multiple *guest OSs* environments simultaneously. A guest OS is an OS executing inside of a VM, i.e., a virtualized OS. In this dissertation, the term guest OS will be used to distinguish between virtualized and non-virtualized OSs. The second taxonomy level is based on whether the guest and host execute the same instruction set architecture (ISA). Multiprogrammed OSs are a typical example of process VMs that execute the same ISA. Process VMs for different ISA needs to emulate program binaries compiled to a different ISA. Two techniques can be applied to perform emulation:

- Interpretation: Fetches, decodes and emulates the execution of individual source instructions. This technique results in a huge performance impact because each instruction requires many native instructions to be emulated.

- Dynamic Binary Translation: Blocks of source instructions are translated into native instructions. This technique increases the performance because the translated blocks can be cached and repeatedly executed without requiring new translation.

Interpretation and binary translation have different performance profiles [70]. Interpretation has lower startup overhead but greater overhead for overall execution. On the other hand, binary translation has high initial overhead in order to translate the instructions

Figure 2.1: A taxonomy of Virtual Machines. Classic-system VMs are the subject of study of this dissertation. Adapted from [70].

for the first time. Thus, some VMs use both techniques combined with a heuristic to determine which source instruction blocks will be interpreted or translated. The best example of a process virtual machine is the Java Virtual Machine [46]. Java is a high-level language (HLL) designed for portability. The Java compiler generates a portable intermediate ISA that can be emulated by the Java Virtual Machine (JVM) for different host ISAs.

In system VMs, the virtualization software is often called a *virtual machine monitor* (VMM) or simply *hypervisor*. System VMs designed to support different ISAs need to emulate all software (OSs and applications). Thus, they are also called whole-system VMs. There are important applications for this kind of VM. For example, an ARM platform including the processor, memory and peripherals can be fully emulated on an Intel IA-32 processor. Thus, the designers can test their software without the target hardware. Additionally, a legacy software can be supported by newer platforms without requiring engineering work to port. An example of a system VM for different ISAs is the QEMU [11]. QEMU is an open source application that can be used either as an emulator or virtualizer. As an emulator, it can run OSs and programs compiled for different ISAs. When used as a virtualizer, it can execute the guest OS code directly on the host CPU. Another example is Open Virtual Platforms (OVP)<sup>1</sup> designed to accelerate embedded software development allowing hardware platforms to be described in C language. Thus, the designers can describe their custom platform, testing and debug their software without the real target.

<sup>&</sup>lt;sup>1</sup>http://www.ovpworld.org/

System VMs to the same ISA, also called classic-system VMs, were developed during the 1960s and they were the first application of virtual machines. At that time, mainframe computer systems were large and expensive. Thus, computers needed to be shared among users. Different users sometimes required different OSs creating the first practical application for virtualization. With the popularization of PCs, interest in classic-system VMs was lost. However, during the 1990s with the appearance of server farms, the classic-system virtualization became popular once again. In this case servers are shared among several users and VMs are a secure way of partitioning the user's software. Classic-system VMs have a lower performance impact when compared to whole-system VMs because the hardware directly executes the VM's instructions.

Recently, the interest in classic-system VMs for embedded systems has increased. However, classic-system VM as applied to server virtualization does not fit directly with ESs. Their intrinsic characteristics as discussed in Section 2.1 motivated the study of new approaches for virtualization on ESs. Thus, the subject of this dissertation is classic-system VMs for embedded systems. Hereafter, the term virtual machine refers to classic-system VMs, unless otherwise noted.

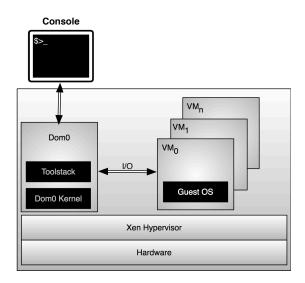

# 2.2.1 Types of Hypervisors

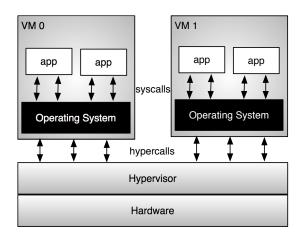

Virtualizing software (VMM or hypervisor) can be divided into two different kinds called *type 1* and *type 2*. Figure 2.2 depicts both. Type 1 hypervisors are also called *native* or *bare-metal* hypervisors. The virtualization layer is implemented between the hardware and the guest OSs, i.e., there is no native OS executing in a system that adopts type 1 virtualization as shown in Figure 2.2(a). A representative type 1 hypervisor is Xen (see Section 3.1). A type 2 hypervisor is implemented as a distinct software layer on top of an existing OS (see Figure 2.2(b)). From the point of view of the underlying OS, it is treated as a normal process and is subject to the same scheduler policies as other user and system processes. In this kind of virtualization, a guest OS can coexist along with the non-virtualized user processes. A representative type 2 hypervisor is KVM (see Section 3.2).

When a home/office user desires to utilize virtualization for some purpose, type 2 hypervisors are most popular. The type 2 hypervisor is installed as a user's application on the existing OS. This technique allows the user to execute a guest OS along with other user

applications. Thus, the guest OS is competing with user applications for system resources, and it is submitted to the same host OS policies as any other process. In terms of memory requirements, type 1 hypervisors are more efficient than type 2 since there is not the overhead of the host OS. Additionally, the hypervisor has the freedom to control all system resources. The main application for type 1 hypervisors is to execute multiple OSs on the same computer, which makes it the perfect choice for server consolidation.

(b) Type 2 hypervisor.

Figure 2.2: Types of hypervisors.

Type 1 and type 2 hypervisors are available for embedded virtualization. However, most type 2 hypervisors used in embedded virtualization were designed for desktop virtualization and adapted for embedded systems. As presented in the Chapter 3, hypervisors designed specifically for embedded systems tend to implement the type 1 approach. Due to restrictions such as memory footprint and real-time constraints, the type 1 model fits embedded systems better. The virtualization model for ESs proposed in this dissertation depicts a type 1 hypervisor.

# 2.2.2 Requirements for Processor's Virtualization

The classic paper written by Popek and Goldberg [60] formalizes the conditions for a processor architecture to be efficiently virtualized. Efficient virtualization means that a VM can be constructed over the processor's architecture without the necessity of modifying the guest OS. In order to understand their theorem, it is necessary to define the difference between control-sensitive, behavior-sensitive and privileged instructions. Control-sensitive instructions can change the configuration of the system's resources, while, behavior-sensitive instructions depend on the configuration of the resources. Instructions that are neither control-sensitive nor behavior-sensitive are termed innocuous [70]. Moreover, instructions that trap the OS when executed in user mode are called privileged instructions. In a hypervisor, any instruction that attempts to change the configuration of the system's resources must be intercepted and emulated accordingly. This is possible when two requirements are accomplished:

- The instruction was executed in user-mode and;

- The control-sensitive and behavior-sensitive instructions are privileged instructions too.

The first requirement is easily accomplished executing the hypervisor in kernel-mode and the guest OS in user-mode. However, the second requirement relies on the processor's architecture. Thus, Popek and Goldberg stated their theorem:

**Theorem 1.** "For any conventional processor a virtual hypervisor may be constructed if the set of sensitive instructions for that computer is a subset of the set of privileged instructions.

Figure 2.3 depicts the theorem. In Figure 2.3(a) the control-sensitive instructions are not a subset of the privileged instructions, i.e., some of them can be executed in user-mode without trapping the hypervisor. This case violates Popek-Goldberg's theorem and cannot be efficiently virtualized. On the other hand, Figure 2.3(b) shows the control-sensitive instructions as a subset of the privileged instructions resulting in a processor that can be efficiently virtualized.

Para-virtualization (see Subsection 2.3.1) can be applied when the processor's architecture is not compatible with the Popek-Goldberg theorem. Thus, allowing a hypervisor implementation for that architecture. Alternatively, processors that support Popek-

Figure 2.3: Illustrating Popek and Goldbergs's Theorem. Adapted from [70].

Goldberg's theorem can be fully-virtualized (see Subsection 2.3.2). Section 2.3 explains the difference between para-virtualization, full-virtualization and hardware-assisted virtualization.

# 2.3 Enabling Techniques and Technologies for Virtualization

The evolution of virtualization technology has resulted in several different approaches. The variety of processor architectures and the appearance of new applications with different needs, has driven techniques that can deliver virtualization on almost all devices. This section describes the three main techniques adopted for hypervisor implementation: para-virtualization (Subsection: 2.3.1), full-virtualization (Subsection 2.3.2) and hardware-assisted virtualization (Subsection 2.3.3). These techniques can be adopted separately or through a hybrid approach, combining two or more of them. The virtualization model and the resulting hypervisor implementation, which is the subject of this work, are a combination of these three techniques.

#### 2.3.1 Para-virtualization

Hypervisors for processor architectures that do not fit Popek and Goldberg's theorem, as explained in Subsection 2.2.2, require different approaches. These architectures

have control-sensitive instructions that do not trap the hypervisor. Therefore, the hypervisor cannot avoid an application changing the processor's behavior. There are two ways to avoid this problem: dynamic binary translation or para-virtualization (PV). Hypervisors that perform dynamic binary translation need to read the VM's instruction prior to their execution in order to emulate the control-sensitive instructions that do not trap the hypervisor. Thus, causing a significant performance penalty when compared to PV. Para-virtualization is a technique that requires modifying and recompiling the guest OS prior to its installation in a VM. These modifications consist of substituting control-sensitive instructions or other OS parts, like the I/O subsystem, by hypercalls. However, for proprietary software or other situations where the source code is not available, the only alternative is dynamic binary translation.

Hypercalls are services provided by the hypervisor and invoked from the guest OS. They are equivalent to system calls (syscalls) in an OS and Figure 2.4 describes their relationship. In operating systems, functions that can only be performed by the OS, like memory allocation or access to the file-system, result in calls to the OS. Similarly, functions that can only be performed by the hypervisor, such as the execution of control-sensitive instructions, can be converted to hypercalls.

Figure 2.4: Relation between hypercalls on a virtualized system and syscalls on a typical operating system.

PV is not limited to processor architectures that cannot support Popek and Goldberg's theorem. In fact, it can extend hypervisor capabilities. For example, PV can be used to implement communication between the VM and the hypervisor or inter-VM communication. Another application for PV is to improve performance, since fully-virtualized hypervisors have a performance issue. If the VM executes control-sensitive instructions constantly, it will

result in an excessive number of traps to the hypervisor, impacting performance. Thus, the OS can be modified to substitute these instructions with hypercalls.

The main limitation of para-virtualization is the engineering work needed to modify the OS to execute in a specific hypervisor. When utilized as a method to extend the capabilities of a virtualized platform, e.g., to support inter-VM communication, PV can be applied as a loadable module. Usually modern operating systems support kernel modules [17], i.e., executable code that can be dynamically loaded into an OS's kernel to add new functionalities. For example, an inter-VM communication module can be added without modifying the OS's source code. VirtlO [64] is a effort to standardize the I/O interfaces for Linux hypervisors consisting of a set of Linux modules. However, para-virtualization used as a method to provide CPU virtualization, i.e., to avoid control-sensitive instructions, requires modifications to the OS's kernel. These modifications must be compatible with the hypervisor's requirements making them unique.

#### 2.3.2 Full-virtualization

The full-virtualization technique requires that the processor architecture fits with the Popek-Goldberg's theorem to implement a virtual machine able to execute a guest OS without any modification. All privileged instructions must be emulated by the hypervisor. Full-virtualization allows the guest OS to be completely decoupled from the virtualization layer. Hence, the guest OS does not need to be modified to be virtualized. Unmodified guests are advantageous because they avoid additional engineering work. However, if the number of emulated privileged instructions are excessive, a fully-virtualized system can suffer from performance penalties. Due to this, para-virtualization was widely adopted in the first generation of embedded hypervisors.

Para-virtualization and full-virtualization can coexist in a combined approach. This approach consists of fully-virtualizing the CPU and uses para-virtualization for certain peripherals or hypercalls for special services. For example, a network device may be para-virtualized to be shared among guest OSs or the hypervisor may implement a hypercall for a guest OS to change its execution priority. Additionally, the designers can implement hypercalls to substitute only instructions that generate an excessive number of traps and to

use emulation for the remaining instructions. However, this requires prior study to determine what instructions must be substituted.

#### 2.3.3 Hardware-assisted Virtualization

This section offers a brief description of typical virtualization extensions. Dedicated hardware for virtualization can simplify hypervisor design and to improve performance and security. However, these advantages require additional hardware support increasing the processor complexity, cost and power consumption. These factors are critical for the ES market. Usually, the specification of virtualization extensions describes a full set of hardware features. However, this set of features must be flexible enough to allow for partial implementation. Thus, the processor's manufacturer can determine the level of hardware-assisted support based on the necessity of the market. For example, limited hardware support may still allow for full-virtualization, but offers poor performance speed-up. In this scenario, the hypervisor must deal with the absence of features to support different processor models. Following is describe three important hardware features typically available in virtualization extensions sets.

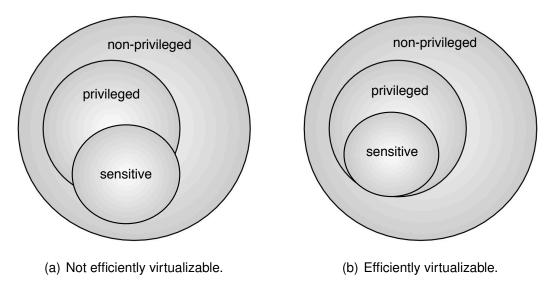

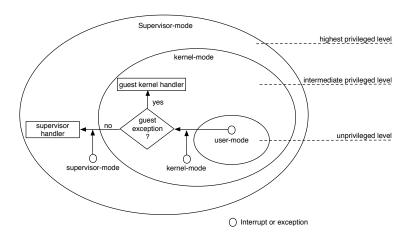

### Additional Privilege Levels

The typical para-virtualization approach on processors without proper virtualization support suffers from the inability to isolate the guest OSs' kernel and user-space. The hypervisor is typically executed in kernel-mode and the entire guest OS is executed in user-mode. As a result, there is no memory isolation between the guest kernel and applications. Thus, a misbehavior or malicious application can disrupt the entire guest OS. A secondary effect is the excessive number of traps generated by the guest OS executing in user-space. This effect can be reduced with PV.

Adding new privilege levels to the processor allows the guest OS to be executed in both kernel and user-modes, since the hypervisor is located in a higher privileged level. Figure 2.5 shows the model of a processor implementing a third privilege level called supervisor. Beyond allowing memory isolation inside the guest OS, the additional privilege level allows one to distinguish between user, kernel and supervisor exceptions. User exceptions,

like system calls, can be handled directly by the guest OS kernel without the necessity to trap the hypervisor. Also, the hypervisor may control the accessibility of some hardware features, like configuration register or instructions, to the guest OS. Thus, the hypervisor may choose a policy of less intervention or a more controlled guest OS.

Figure 2.5: Supervisor privileged level for hypervisor execution.

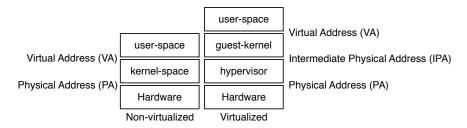

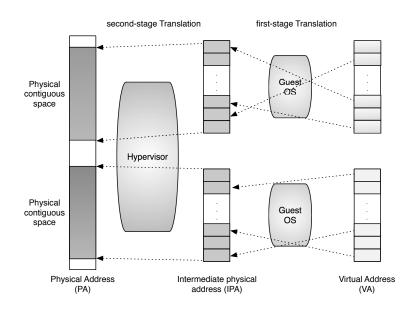

### 2-Stage TLB Translation

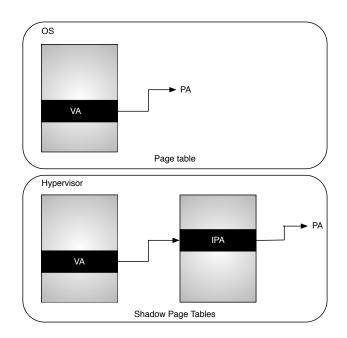

Processors targeting GPOSs rich in features must support a memory management unit (MMU) to provide a virtual memory mechanism. Thus, the OS can implement memory isolation between processes increasing software reliability and security. Translation lookaside buffer (TLB) is a common hardware construction to assist MMU, which works like a page table cache. High performance processors can automatically performs page walks in the page table when a TLB miss occurs, i.e., the target address is not found in TLB. However, simpler processors will trap the OS in this situation. Thus, the OS must handle a TLB exception to reconfigure the TLB cache. In a virtualized system, the hypervisor must virtualize the MMU keeping the guest OSes isolated from each other, which requires a second stage of address translation. Figure 2.6(a) shows the difference between virtual memory translation in a non-virtualized versus a virtualized system. In a non-virtualized system, the OS translates virtual addresses (VAs) to physical addresses (PAs) using its page table to configure the TLB. In a virtualized system, VAs are translated to intermediate physical addresses (IPAs), which must be managed by the hypervisor. Processors without the proper virtualization support require the hypervisor to implement a technique called shadow page tables that keeps the correct translation from IPA to PA. Figure 2.6(b) represents the difference between an OS page table and a hypervisor shadow page tables. When using this

technique, the guest OS still manages its page tables, but it cannot configure the processor's TLB directly. The hypervisor handles the page faults reading the address mapping from the guest OS and creating its shadow page table. This second-stage address translation performed by software generates an excessive number of hypervisor exceptions, since, the TLB configuration involves privileged instructions. Again, the number of exceptions can be reduced using hypercalls.

(a) Non-virtualized versus virtualized virtual memory address translation.

(b) OS page table versus hypervisor shadow page tables.

Figure 2.6: Memory virtualization approaches in non-virtualized versus virtualized systems.

Current virtualization extensions for embedded processor families, like MIPS and ARM, implement a second-stage TLB translation in hardware. Essentially, the hardware performs the translation from IPA to PA without software intervention. The hypervisor still manages its page table mapping IPA to PA. However, the guest OS is allowed to configure directly the TLB. This is possible because the two TLB stages are configured from different processor modes. For example, the hypervisor (supervisor-mode) configures the second-